FER u europskom projektu HPC i AI autonomije

Projekt Digitalna autonomija sa RISC-V u Europi, posebni ugovor 1 službeno započinje kao revolucionarna inicijativa za jačanje europske tehnološke neovisnosti u HPC i AI područjima

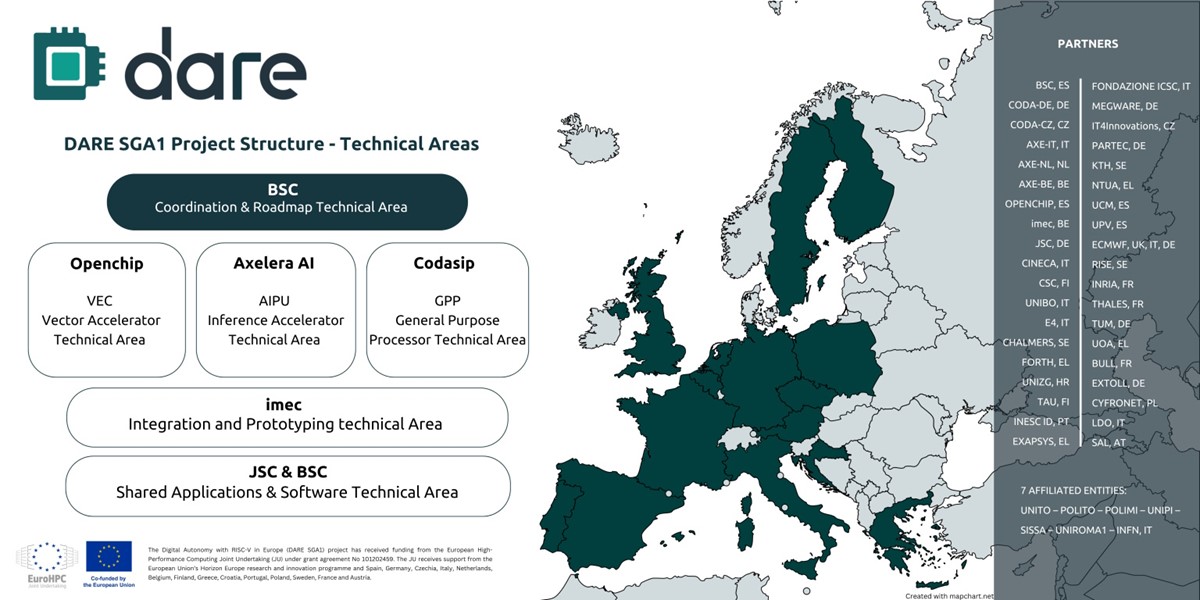

S potporom Zajedničkog poduzeća za europsko računalstvo visokih performansi (European High Performance Computing Joint Undertaking - EuroHPC JU) i pod koordinacijom Barcelona Supercomputing Center (BSC-CNS), DARE SGA1 ujedinjuje 38 vodećih partnera iz cijele Europe. Oni će zajedno razviti procesore i računalne sustave iduće generacije, projektirane za primjene u istraživanju i industriji.

Digitalna neovisnost

S budžetom prve faze od 240 milijuna eura, ovaj ambiciozni trogodišnji projekt označava prvu fazu šestogodišnje inicijative. Cilj DARE SGA1 je izgraditi potpuno europsko super računalno okruženje, s procesorima visokih performansi i energetske učinkovitosti, koji su projektirani i razvijani u Europi. Ta je inicijativa direktan odgovor na europsku stratešku potrebu za digitalnom neovisnošću, koja će osigurati da Europa ostane u potpunoj kontroli nad svojom kritičnom računalnom infrastrukturom.

Europa je već predugo ovisna o hardverskim i softverskim rješenjima za infrastrukturu računarstva visokih performansi koja nisu europskog porijekla. Takva ovisnost predstavlja rizik za sigurnost, ekonomsku stabilnost i tehnološku kompetitivnost. Namjera je projekta DARE SGA1 preokrenuti taj trend tako da iskoristi otvoreni RISC-V ekosustav i chiplet tehnologiju, i tako stvori istinski europske proizvode koji će biti ključni dio budućih europskih superračunala.

Ključne tehnološke inovacije

U samom srcu DARE projekta razvoj je tri chipleta zasnovana na RISC-V specifikaciji, gdje svaki od njih obnaša kritičnu funkciju u HPC-u i AI računarstvu:

- Vektorski akcelerator (VEC) za HPC visoke preciznosti i aplikacija koje tek nastaju u domeni konvergencije HPC-AI, pod vodstvom Openchipa

- Procesor za umjetnu inteligenciju (AI Processing Unit – AIPU) dizajniran za ubrzanje inferencije algoritama umjetne inteligencije kod HPC aplikacija, pod vodstvom Axelera AI

- Procesor opće namjene (General-purpose Processor - GPP) optimiran za izvođenje HPC zadataka u europskim superračunalima, pod vodstvom Codasipa

Ti će chipleti biti razvijeni i proizvedeni koristeći napredne CMOS tehnološke procese, tako da prevladaju ograničenja tradicionalnih monolitnih čipova kroz višu učinkovitost, skalabilnost i financijsku isplativost.

Kako bi se osigurao uspjeh ovih inovacija, DARE SGA1 koristi pristup kodizajna hardvera i softvera, preko izabranog seta europskih HPC i AI aplikacija. Potpuni softverski stog, optimiziran za DARE SGA1 hardver, bit će razvijen paralelno s razvojem hardvera, koristeći rani pristup RISC-V sklopovskoj emulaciji i simulaciji. Usto, DARE će uključiti aktivnosti istraživačkog softverskog i hardverskog dizajna za blisku budućnost, kao i utiranje puteva za studije skalabilnosti za ugradnju projektiranih procesora u buduća superračunala.

Sudjelovanje FER-a

U okviru projekta DARE SGA1, Fakultet elektrotehnike i računarstva sa svojim Razvojnim centrom za arhitekture i aplikacije računala visokih performansi nastavlja stratešku suradnju s europskim partnerima na razvoju najnovijih generacija procesora kojima se želi postići europska tehnološka neovisnost.

„FER-ovi istraživači već dugi niz godina dio su vodeće EU industrijsko-istraživačke grupe koja ima cilj razviti nove generacije globalno komercijalno konkurentnih procesora i akceleratora za računarstvo visokih performansi i umjetnu inteligenciju zasnovanih na RISC-V skupu naredaba. Aktivnosti te grupe prepoznati su od strane EU i rezultirali su u pokretanju jednog od najvećih industrijsko-razvojnih projekata na području računarstva. FER će u okviru projekta sudjelovati u raznim aktivnostima, no naš je glavni fokus razvoj najnaprednije vektorske jedinice s protočnom arhitekturom za operacije nad realnim brojevima (vector floating point unit - VFPU). Taj projekt nastavak je naših aktivnosti na drugim strateškim EU projektima razvoja procesora kojim je EU predstavila svoju odlučnost u uspostavljanju tehnološke izvrsnosti. Računarstvo visokih performansi i umjetna inteligencija kritična su područja za konkurentnost svih grana industrije i istraživanja, gotovo svih aktivnosti bitnih za građane, poput zdravstva, energije, te društva u cjelini. Naši istraživački rezultati će biti uključeni u procesore koji će biti ugrađeni u neke od najvećih EU računalnih sustava i na taj način pomoći u ostvarivanju tehnološke suverenosti EU,“ naglasio je direktor Razvojnog centra za arhitekture i aplikacije računala visokih performansi Fakulteta elektrotehnike i računarstva i voditelj hrvatskog dijela konzorcija prof. dr. sc. Mario Kovač.

Konzorcij

Konzorcij sačinjen od 38 europskih partnera, pod vodstvom BSC-CNS-a, surađuje na DARE SGA1 projektu kako bi poboljšali digitalnu autonomiju u područjima HPC-a i AI-ja.

Uz već ranije spomenute Openchip, Axelera AI i Codasip, imec i Jülich Supercomputing Centre (JSC) pri Forschungszentrum Jüulich će djelovati kao tehničko vodstvo, upravljajući ključnim inovacijama unutar projekta. Usto što ima ulogu glavnog koordinatora, BSC će također voditi određivanje puteva razvoja i VEC istraživanje, uz rad na aktivnostima razvoja softvera i hardvera. Kolektivni napori svih partnera su visokovrijedni, jer predstavljaju ključnu ulogu u napredovanju europske neovisnosti u području HPC-a i AI-ja.

Put u post-egzaskalarno računarstvo

Prema kraju prve faze, DARE SGA1 će utrti put za prvi potpuno europski HPC sustav, promovirajući tehnološku samodostatnost i osiguravajući da europska industrija, istraživanje i društvo mogu koristiti sigurna i energetski učinkovita rješenja računarstva visokih performansi.

DARE SGA1 nije samo vezan uz tehnološki razvoj – on se tiče i definiranja puta europskih superračunala za post-egzaskalarno računarstvo. Projekt će utrti put za buduće generacije superračunala koja će biti dizajnirana, izrađivana i optimizirana u Europi, osiguravajući na taj način da Europa ostane u samom vrhu razvoja HPC i AI.